# LM1972

# $\mu$ Pot<sup>TM</sup> 2-Channel 78dB Audio Attenuator with Mute

# **General Description**

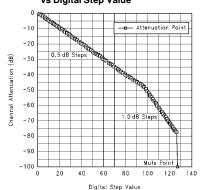

The LM1972 is a digitally controlled 2-channel 78dB audio attenuator fabricated on a CMOS process. Each channel has attenuation steps of 0.5dB from 0dB-47.5dB, 1.0dB steps from 48dB-78dB, with a mute function attenuating 104dB. Its logarithmic attenuation curve can be customized through software to fit the desired application.

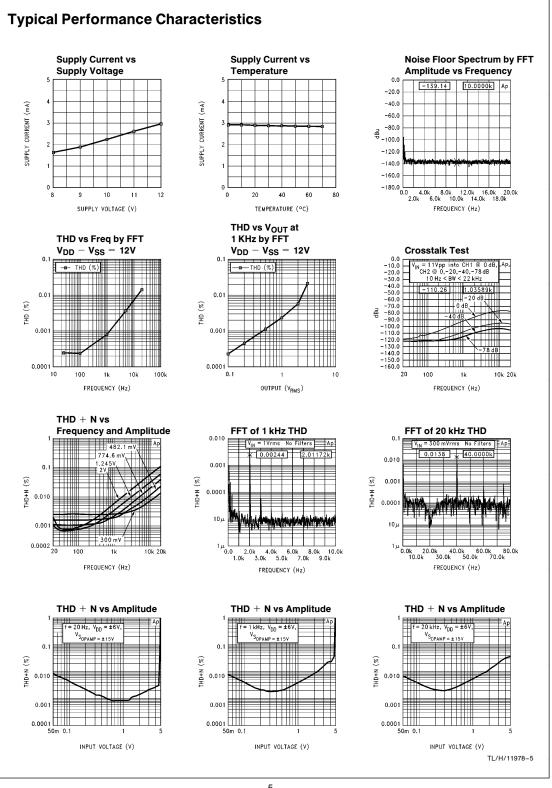

The performance of a  $\mu Pot$  is demonstrated through its excellent Signal-to-Noise Ratio, extremely low (THD+N), and high channel separation. Each  $\mu Pot$  contains a mute function that disconnects the input signal from the output, providing a minimum attenuation of 96dB. Transitions between any attenuation settings are pop free.

The LM1972's 3-wire serial digital interface is TTL and CMOS compatible; receiving data that selects a channel and the desired attenuation level. The Data-Out pin of the LM1972 allows multiple  $\mu \text{Pots}$  to be daisy-chained together, reducing the number of enable and data lines to be routed for a given application.

# **Key Specifications**

■ Total Harmonic Distortion + Noise 0.003% (max)

■ Frequency response 100 kHz (-3dB) (min)

■ Attenuation range (excluding mute) 78dB (typ)

■ Differential attenuation ±0.25dB (max)

■ Signal-to-noise ratio (ref. 4 Vrms) 110dB (min)

■ Channel separation 100dB (min)

### **Features**

- 3-wire serial interface

- Daisy-chain capability

- 104dB mute attenuation

- Pop and click free attenuation changes

# **Applications**

- Automated studio mixing consoles

- Music reproduction systems

- Sound reinforcement systems

- Electronic music (MIDI)

- Personal computer audio control

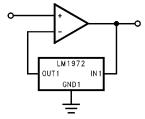

# **Typical Application**

# AUDIO OUT#1 AUDIO OUT#2

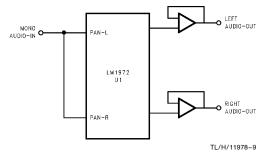

FIGURE 1. Typical Audio Attenuator Application Circuit

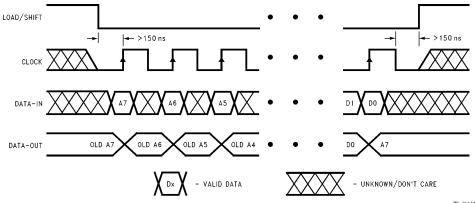

# **Connection Diagram**

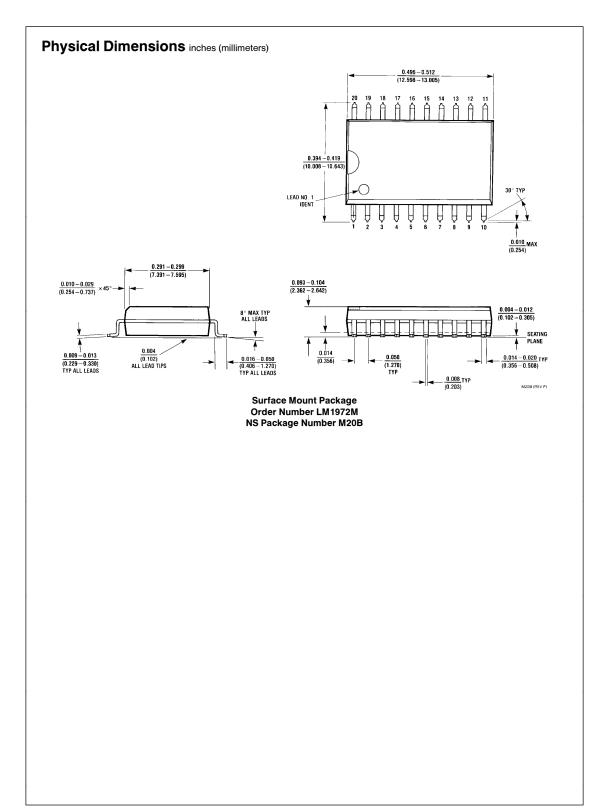

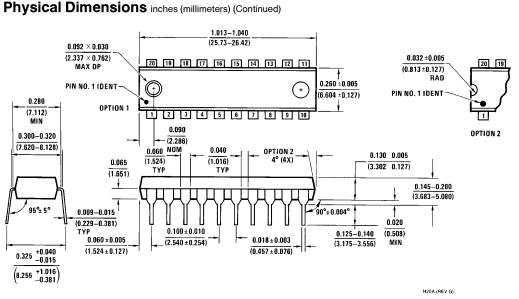

### Dual-In-Line Plastic or Surface Mount Package

Top View

Order Number LM1972M or LM1972N See NS Package Number M20B or N20A

$\mu Pot^{TM}$  and Overture  $^{TM}$  are trademarks of National Semiconductor Corporation.

# **Absolute Maximum Ratings** (Notes 1, 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage ( $V_{DD}-V_{SS}$ ) Voltage at Any Pin  $\rm V_{SS}-0.2V$  to  $\rm V_{DD}+0.2V$ Power Dissipation (Note 3) 150 mW ESD Susceptability (Note 4) 2000V

150°C

Soldering Information N Package (10 sec.) Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$

# Operating Ratings (Notes 1, 2)

$T_{MIN}$  $T_{MAX}$ Temperature Range  $T_{MIN} \le T_{A} \le T_{MAX}$ Supply Voltage (V<sub>DD</sub> - V<sub>SS</sub>) 0°C  $\leq$  +70°C 4.5V to 12V

+260°C

# **Electrical Characteristics** (Notes 1, 2)

Junction Temperature

The following specifications apply for all channels with  $V_{DD} = +6V$ ,  $V_{SS} = -6V$ ,  $V_{IN} = 5.5$  Vpk, and f = 1 kHz, unless otherwise specified. Limits apply for  $T_A = 25$ °C. Digital inputs are TTL and CMOS compatible.

| Symbol         | Parameter                                     |                                                                                                   | LM1972                               |                                     | 11                                                       |

|----------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------|----------------------------------------------------------|

|                |                                               | Conditions                                                                                        | Typical<br>(Note 5)                  | Limit<br>(Note 6)                   | Units<br>(Limits)                                        |

| Is             | Supply Current                                | Inputs are AC Grounded                                                                            | 2                                    | 4                                   | mA (max)                                                 |

| THD+N          | Total Harmonic Distortion plus Noise          | V <sub>IN</sub> = 0.5 Vpk @ 0dB Attenuation                                                       | 0.0008                               | 0.003                               | % (max)                                                  |

| XTalk          | Crosstalk (Channel Separation)                | 0dB Attenuation for V <sub>IN</sub><br>V <sub>CH</sub> measured @ -78dB                           | 110                                  | 100                                 | dB (min)                                                 |

| SNR            | Signal-to-Noise Ratio                         | Inputs are AC Grounded @ -12dB Attenuation A-Weighted                                             | 120                                  | 110                                 | dB (min)                                                 |

| A <sub>M</sub> | Mute Attenuation                              |                                                                                                   | 104                                  | 96                                  | dB (min)                                                 |

|                | Attenuation Step Size Error                   | 0dB to -47.5dB<br>-48dB to -78dB                                                                  |                                      | ±0.05<br>±0.25                      | dB (max)<br>dB (max)                                     |

|                | Absolute Attenuation Error                    | Attenuation @ 0dB Attenuation @ -20dB Attenuation @ -40dB Attenuation @ -60dB Attenuation @ -78dB | 0.03<br>19.8<br>39.5<br>59.3<br>76.3 | 0.5<br>19.0<br>39.0<br>57.5<br>74.5 | dB (min)<br>dB (min)<br>dB (min)<br>dB (min)<br>dB (min) |

|                | Channel-to-Channel Attenuation Tracking Error | Attenuation @ 0dB, -20dB, -40dB, -60dB<br>Attenuation @ -78dB                                     |                                      | ±0.5<br>±0.75                       | dB (max)<br>dB (max)                                     |

| ILEAK          | Analog Input Leakage Current                  | Inputs are AC Grounded                                                                            | 10.0                                 | 100                                 | nA (max)                                                 |

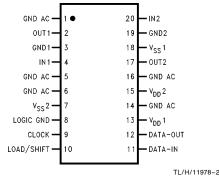

FIGURE 2. Timing Diagram

TL/H/11978-3

# **Electrical Characteristics** (Notes 1, 2)

The following specifications apply for all channels with  $V_{DD}=+6V$ ,  $V_{SS}=-6V$ ,  $V_{IN}=5.5$  Vpk, and f=1 kHz, unless otherwise specified. Limits apply for  $T_A=25^{\circ}C$ . Digital inputs are TTL and CMOS compatible. (Continued)

|                  | Parameter                |                                                  | LM1972              |                   | Units                           |

|------------------|--------------------------|--------------------------------------------------|---------------------|-------------------|---------------------------------|

| Symbol           |                          | Conditions                                       | Typical<br>(Note 5) | Limit<br>(Note 6) | (Limits)                        |

| R <sub>IN</sub>  | AC Input Impedance       | Pins 4, 20, V <sub>IN</sub> = 1.0 Vpk, f = 1 kHz | 40                  | 20<br>60          | $k\Omega$ (min) $k\Omega$ (max) |

| I <sub>IN</sub>  | Input Current            | @ Pins 9, 10, 11 @ 0V < V <sub>IN</sub> < 5V     | 1.0                 | ± 100             | nA (max)                        |

| f <sub>CLK</sub> | Clock Frequency          |                                                  | 3                   | 2                 | MHz (max)                       |

| V <sub>IH</sub>  | High-Level Input Voltage | @ Pins 9, 10, 11                                 |                     | 2.0               | V (min)                         |

| $V_{IL}$         | Low-Level Input Voltage  | @ Pins 9, 10, 11                                 |                     | 0.8               | V (max)                         |

|                  | Data-Out Levels (Pin 12) | V <sub>DD</sub> =6V, V <sub>SS</sub> =0V         |                     | 0.1<br>5.9        | V (max)<br>V (min)              |

Note 1: All voltages are measured with respect to GND pins (1, 3, 5, 6, 14, 16, 19), unless otherwise specified.

Note 2: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guaranteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

Note 3: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$ ,  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable power dissipation is PD =  $(T_{JMAX} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For the LM1972,  $T_{JMAX} = +150^{\circ}\text{C}$ , and the typical junction-to-ambient thermal resistance, when board mounted, is 65°C/W.

Note 4: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 5: Typicals are measured at 25°C and represent the parametric norm.

Note 6: Limits are guaranteed to National's AOQL (Average Output Quality Level).

# **Pin Description**

**Signal Ground (3, 19):** Each input has its own independent ground, GND1 and GND2.

Signal Input (4, 20): There are 2 independent signal inputs, IN1 and IN2.

**Signal Output (2, 17):** There are 2 independent signal outputs, OUT1 and OUT2.

Voltage Supply (13, 15): Positive voltage supply pins,  $V_{DD1}$  and  $V_{DD2}.$

**Voltage Supply (7, 18):** Negative voltage supply pins,  $V_{SS1}$  and  $V_{SS2}$ . To be tied to ground in a single supply configuration.

AC Ground (1, 5, 6, 14, 16): These five pins are not physically connected to the die in any way (i.e., No bondwires). These pins must be AC grounded to prevent signal coupling between any of the pins nearby. Pin 14 should be connected to pins 13 and 15 for ease of wiring and the best isolation, as an example.

**Logic Ground (8):** Digital signal ground for the interface lines; CLOCK, LOAD/SHIFT, DATA-IN and DATA-OUT.

Clock (9): The clock input accepts a TTL or CMOS level signal. The clock input is used to load data into the internal shift register on the rising edge of the input clock waveform.

**Load/Shift (10):** The load/shift input accepts a TTL or CMOS level signal. This is the enable pin of the device, allowing data to be clocked in while this input is low (0V).

**Data-In (11):** The data-in input accepts a TTL or CMOS level signal. This pin is used to accept serial data from a microcontroller that will be latched and decoded to change a channel's attenuation level.

**Data-Out (12):** This pin is used in daisy-chain mode where more than one  $\mu$ Pot is controlled via the same data line. As the data is clocked into the chain from the  $\mu$ C, the preceding data in the shift register is shifted out the DATA-OUT pin to the next  $\mu$ Pot in the chain or to ground if it is the last  $\mu$ Pot in the chain. The LOAD/SHIFT line goes high once all of the new data has been shifted into each of its respective registers

# **Connection Diagram**

TL/H/11978-4

# **Application Information**

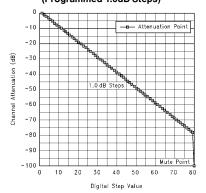

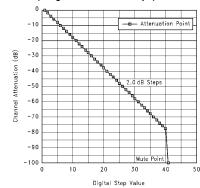

### ATTENUATION STEP SCHEME

The fundamental attenuation step scheme for the LM1972  $\mu$ Pot is shown in *Figure 3.* This attenuation step scheme, however, can be changed through programming techniques to fit different application requirements. One such example would be a constant logarithmic attenuation scheme of 1dB steps for a panning function as shown in Figure 4. The only restriction to the customization of attenuation schemes are the given attenuation levels and their corresponding data bits shown in Table I. The device will change attenuation levels only when a channel address is recognized. When recognized, the attenuation level will be changed corresponding to the data bits shown in Table I. As shown in Figure 6, an LM1972 can be configured as a panning control which separates the mono signal into left and right channels. This circuit may utilize the fundamental attenuation scheme of the LM1972 or be programmed to provide a constant 1dB logarithmic attenuation scheme as shown in Figure 4.

# LM1972 Channel Attenuation vs Digital Step Value

TL/H/11978-6

FIGURE 3. LM1972 Attenuation Step Scheme

### LM1972 Channel Attenuation vs Digital Step Value (Programmed 1.0dB Steps)

TL/H/11978-7 FIGURE 4. LM1972 1.0dB

**Attenuation Step Scheme**

# LM1972 Channel Attenuation vs Digital Step Value (Programmed 2.0dB Steps)

TL/H/11978-8

FIGURE 5. LM1972 2.0dB Attenuation Step Scheme

FIGURE 6. Mono Panning Circuit

# INPUT IMPEDANCE

The input impedance of a  $\mu Pot$  is constant at a nominal 40 k $\Omega.$  To eliminate any unwanted DC components from propagating through the device it is common to use 1  $\mu F$  input coupling caps. This is not necessary, however, if the dc offset from the previous stage is negligible. For higher performance systems, input coupling caps are preferred.

### **OUTPUT IMPEDANCE**

The output of a  $\mu Pot$  varies typically between 25 k $\Omega$  and 35 k $\Omega$  and changes nonlinearly with step changes. Since a  $\mu Pot$  is made up of a resistor ladder network with a logarithmic attenuation, the output impedance is nonlinear. Due to this configuration, a  $\mu Pot$  cannot be considered as a linear potentiometer, but can be considered only as a logarithmic attenuator

It should be noted that the linearity of a  $\mu Pot$  cannot be measured directly without a buffer because the input impedance of most measurement systems is not high enough to provide the required accuracy. Due to the low impedance of the measurement system, the output of the  $\mu Pot$  would be loaded down and an incorrect reading will result. To prevent loading from occurring, a JFET input op amp should be used as the buffer/amplifier. The performance of a  $\mu Pot$  is limited only by the performance of the external buffer/amplifier.

# **Application Information (Continued)**

### **MUTE FUNCTION**

One major feature of a  $\mu Pot$  is its ability to mute the input signal to an attenuation level of 104dB as shown in Figure 3. This is accomplished internally by physically isolating the output from the input while also grounding the output pin through approximately 2 k $\Omega.$

The mute function is obtained during power-up of the device or by sending any binary data of 01111111 and above (to 11111111) serially to the device. The device may be placed into mute from a previous attenuation setting by sending any of the above data. This allows the designer to place a mute button onto his system which could cause a microcontroller to send the appropriate data to a  $\mu Pot$  and thus mute any or all channels. Since this function is achieved through software, the designer has a great amount of flexibility in configuring the system.

### **DC INPUTS**

Although the  $\mu Pot$  was designed to be used as an attenuator for signals within the audio spectrum, the device is capable of tracking an input DC voltage. The device will track DC voltages to a diode drop above each supply rail.

One point to remember about DC tracking is that with a buffer at the output of the  $\mu Pot$ , the resolution of DC tracking will depend upon the gain configuration of that output buffer and its supply voltage. It should also be remembered that the output buffer's supply voltage does not have to be the same as the  $\mu Pot$ 's supply voltage. This could allow for more resolution when DC tracking.

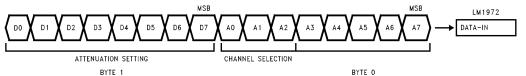

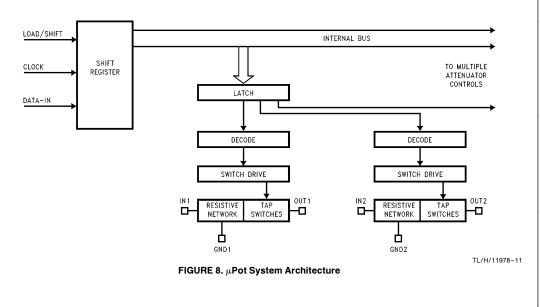

### **SERIAL DATA FORMAT**

The LM1972 uses a 3-wire serial communication format that is easily controlled by a microcontroller. The timing for the 3-wire set, comprised of DATA-IN, CLOCK, and LOAD/SHIFT is shown in *Figure 2. Figure 8* exhibits in block diagram form how the digital interface controls the tap switches which select the appropriate attenuation level. As depicted in *Figure 2*, the LOAD/SHIFT line is to go low at least 150 ns before the rising edge of the first clock pulse and is to remain low throughout the transmission of each set of 16 data bits. The serial data is comprised of 8 bits for channel selection and 8 bits for attenuation setting. For both address data and attenuation setting data, the MSB is sent first and the 8 bits of address data are to be sent before the 8 bits of attenuation data. Please refer to *Figure 7* to confirm the serial data format transfer process.

TABLE I. LM1972 Micropot Attenuator Register Set Description

| MSB                    | LSB                       |                      |  |  |  |  |  |

|------------------------|---------------------------|----------------------|--|--|--|--|--|

|                        | Address Register (Byte 0) |                      |  |  |  |  |  |

| 000                    | 00 0000                   | Channel 1            |  |  |  |  |  |

| 000                    | 00 0001                   | Channel 2            |  |  |  |  |  |

| 000                    | 00 0010                   | Channel 3            |  |  |  |  |  |

| Data Register (Byte 1) |                           |                      |  |  |  |  |  |

| Co                     | ntents                    | Attenuation Level dB |  |  |  |  |  |

| 000                    | 00 0000                   | 0.0                  |  |  |  |  |  |

| 000                    | 00 0001                   | 0.5                  |  |  |  |  |  |

| 000                    | 00 0010                   | 1.0                  |  |  |  |  |  |

| 000                    | 00 0011                   | 1.5                  |  |  |  |  |  |

|                        | ::::                      | ::                   |  |  |  |  |  |

| 000                    | 01 1110                   | 15.0                 |  |  |  |  |  |

| 000                    | 01 1111                   | 15.5                 |  |  |  |  |  |

| 00-                    | 10 0000                   | 16.0                 |  |  |  |  |  |

| 00-                    | 10 0001                   | 16.5                 |  |  |  |  |  |

| 00-                    | 10 0010                   | 17.0                 |  |  |  |  |  |

| :                      | :::::                     | ::                   |  |  |  |  |  |

| 010                    | 01 1110                   | 47.0                 |  |  |  |  |  |

| 010                    | 01 1111                   | 47.5                 |  |  |  |  |  |

| 01                     | 10 0000                   | 48.0                 |  |  |  |  |  |

| 01                     | 10 0001                   | 49.0                 |  |  |  |  |  |

| 01                     | 10 0010                   | 50.0                 |  |  |  |  |  |

|                        | :::::                     | ::                   |  |  |  |  |  |

| 01                     | 11 1100                   | 76.0                 |  |  |  |  |  |

| 01                     | 11 1101                   | 77.0                 |  |  |  |  |  |

| 01                     | 11 1110                   | 78.0                 |  |  |  |  |  |

| 01                     | 11 1111                   | 100.0 (Mute)         |  |  |  |  |  |

| 100                    | 00 0000                   | 100.0 (Mute)         |  |  |  |  |  |

|                        | ::::                      | ::                   |  |  |  |  |  |

| 111                    | 11 1110                   | 100.0 (Mute)         |  |  |  |  |  |

| 111                    | 11 1111                   | 100.0 (Mute)         |  |  |  |  |  |

| •                      |                           | •                    |  |  |  |  |  |

FIGURE 7. Serial Data Format Transfer Process

TL/H/11978-10

# **Application Information (Continued)**

### $\mu$ Pot SYSTEM ARCHITECTURE

The  $\mu\text{Pot}$ 's digital interface is essentially a shift register, where serial data is shifted in, latched, and then decoded. As new data is shifted into the DATA-IN pin, the previously latched data is shifted out the DATA-OUT pin. Once the data is shifted in, the LOAD/SHIFT line goes high, latching in the new data. The data is then decoded and the appropriate switch is activated to set the desired attenuation level for the selected channel. This process is continued each and every time an attenuation change is made. Each channel is updated, only, when that channel is selected for an attenuator change or the system is powered down and then back up again. When the  $\mu\text{Pot}$  is powered up, each channel is placed into the muted mode.

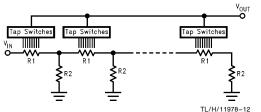

### μPot LADDER ARCHITECTURE

Each channel of a  $\mu Pot$  has its own independent resistor ladder network. As shown in Figure 9, the ladder consists of multiple R1/R2 elements which make up the attenuation scheme. Within each element there are tap switches that select the appropriate attenuation level corresponding to the data bits in Table I. It can be seen in Figure 9 that the input impedance for the channel is a constant value regardless of which tap switch is selected, while the output impedance varies according to the tap switch selected.

FIGURE 9.  $\mu$ Pot Ladder Architecture

### DIGITAL LINE COMPATIBILITY

The  $\mu$ Pot's digital interface section is compatible with either TTL or CMOS logic due to the shift register inputs acting upon a threshold voltage of 2 diode drops or approximately 1.4V.

### **DIGITAL DATA-OUT PIN**

The DATA-OUT pin is available for daisy-chain system configurations where multiple  $\mu \text{Pots}$  will be used. The use of the daisy-chain configuration allows the system designer to use only one DATA and one LOAD/SHIFT line per chain, thus simplifying PCB trace layouts.

In order to provide the highest level of channel separation and isolate any of the signal lines from digital noise, the DATA-OUT pin should be terminated through a  $2~k\Omega$  resistor if not used. The pin may be left floating, however, any signal noise on that line may couple to adjacent lines creating higher noise specs.

8

### **Application Information (Continued)**

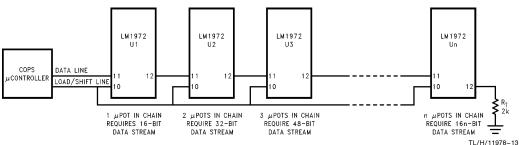

### **DAISY-CHAIN CAPABILITY**

Since the  $\mu$ Pot's digital interface is essentially a shift register, multiple  $\mu$ Pots can be programmed utilizing the same data and load/shift lines. As shown in *Figure 10*, for an n- $\mu$ Pot daisy-chain, there are 16n bits to be shifted and loaded for the chain. The data loading sequence is the same for n- $\mu$ Pots as it is for one  $\mu$ Pot. First the LOAD/SHIFT line goes low, then the data is clocked in sequentially while the preceding data in each  $\mu$ Pot is shifted out the DATA-OUT pin to the next  $\mu$ Pot in the chain or to ground if it is the last  $\mu$ Pot in the chain. Then the LOAD/SHIFT line goes high; latching the data into each of their corresponding  $\mu$ Pots. The data is then decoded according to the address (channel selection) and the appropriate tap switch control-ling the attenuation level is selected.

### **CROSSTALK MEASUREMENTS**

The crosstalk of a  $\mu$ Pot as shown in the **Typical Performance Characteristics** section was obtained by placing a signal on one channel and measuring the level at the output of another channel of the same frequency. It is important to be sure that the signal level being measured is of the same frequency such that a true indication of crosstalk may be obtained. Also, to ensure an accurate measurement, the measured channel's input should be AC grounded through a 1  $\mu$ F capacitor.

### **CLICKS AND POPS**

So, why is that output buffer needed anyway? There are three answers to this question, all of which are important from a system point of view.

The first reason to utilize a buffer/amplifier at the output of a  $\mu Pot$  is to ensure that there are no audible clicks or pops due to attenuation step changes in the device. If an onboard bipolar op amp had been used for the output stage, its requirement of a finite amount of DC bias current for operation would cause a DC voltage "pop" when the output impedance of the  $\mu Pot$  changes. Again, this phenomenon is due to the fact that the output impedance of the  $\mu Pot$  is changing with step changes and a bipolar amplifier requires a finite amount of DC bias current for its operation. As the impedance changes, so does the DC bias current and thus there is a DC voltage "pop".

Secondly, the  $\,\mu Pot$  has no drive capability, so any desired gain needs to be accomplished through a buffer/non-inverting amplifer.

Third, the output of a \$\mu\$Pot needs to see a high impedance to prevent loading and subsequent linearity errors from ocurring. A JFET input buffer provides a high input impedance to the output of the \$\mu\$Pot so that this does not occur. Clicks and pops can be avoided by using a JFET input buffer/amplifier such as an LF412ACN. The LF412 has a high input impedance and exhibits both a low noise floor and low THD+N throughout the audio spectrum which maintains signal integrity and linearity for the system. The performance of the system solution is entirely dependent upon the quality and performance of the JFET input buffer/amplifier.

### LOGARITHMIC GAIN AMPUFIER

The µPot is capable of being used in the feedback loop of an amplifier, however, as stated previously, the output of the μPot needs to see a high impedance in order to maintain its high performance and linearity. Again, loading the output will change the values of attenuation for the device. As shown in Figure 11, a  $\mu$ Pot used in the feedback loop creates a logarithmic gain amplifier. In this configuration the attenuation levels from Table I, now become gain levels with the largest possible gain value being 78dB. For most applications 78dB of gain will cause signal clipping to occur, however, because of the µPot's versatility the gain can be controlled through programming such that the clipping level of the system is never obtained. An important point to remember is that when in mute mode the input is disconnected from the output. In this configuration this will place the amplifier in its open loop gain state, thus resulting in severe comparator action. Care should be taken with the programming and design of this type of circuit. To provide the best performance, a JFET input amplifier should be used.

TL/H/11978-14

FIGURE 11. Digitally-Controlled Logarithmic Gain Amplifier Circuit

FIGURE 10. n- $\mu$ Pot Daisy-Chained Circuit

Dual-In-Line Plastic Package Order Number LM1972N NS Package Number N20A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: 1(800) 272-9959 TWX: (910) 339-9240 National Semiconductor GmbH Livry-Gargan-Str. 10 D-82256 Fürstenfeldbruck Germany Tel: (81-41) 35-0 Telex: 527649 Fax: (81-41) 35-1

Japan Ltd.

Sumitomo Chemical

Engineering Center

Bldg. 7F

1-7-1, Nakase, Mihama-Ku

Chiba-City,

Ciba Prefecture 261

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductores Do Brazil Ltda. Rue Deputado Lacorda Franco 120-3A Sao Paulo-SP Brazil 05418-000 Tel: (55-11) 212-5066 Telex: 391-1131931 NSBR BR Fax: (55-11) 212-1181 National Semiconductor (Australia) Pty, Ltd. Building 16 Business Park Drive Monash Business Park Nottinghill, Melbourne Victoria 3168 Australia Tel: (3) 558-9999 Fax: (3) 558-9998