by F. GRILLI / P. BERGER

# **TECHNICAL INFORMATION**

| 1.  | ABSTRACT                                                                     | 2 |

|-----|------------------------------------------------------------------------------|---|

| 2.  | INTRODUCTION                                                                 | 2 |

| 3.  | FUNCTIONAL DESCRIPTION                                                       | 2 |

| 3.1 | Horizontal oscillator                                                        | 2 |

| 3.2 | Horizontal synchronism shaper circuit.                                       | 2 |

| 3.3 | First phase comparator ( $\varphi$ 1) and phase adjustment interface circuit | 2 |

| 3.4 | Second phase comparator ( $\varphi$ 2) between flyback and oscillator        | 5 |

| 3.5 | Phase shifter, output stage and start up circuit                             | 5 |

| 3.6 | Voltage regulator 8V                                                         | 6 |

| 3.7 | Vertical oscillator                                                          | 6 |

| 3.8 | S Correction circuit and DC linearity adjustment                             | 7 |

| 3.9 | Vertical amplitude regulation circuit                                        | 8 |

| 4.  | CONCLUSION                                                                   | 8 |

# **APPLICATION INFORMATION**

| 5.  | HORIZONTAL SECTION                      | 10 |

|-----|-----------------------------------------|----|

| 5.1 | Frequency                               | 10 |

| 5.2 | Pull-in range                           | 10 |

| 5.3 | Internal sync width                     | 10 |

| 5.4 | Phase adjustment range                  | 10 |

| 5.5 | Flyback input                           | 11 |

| 6.  | VERTICAL SECTION                        | 11 |

| 6.1 | Frequency                               | 11 |

| 6.2 | Pull-in range                           | 11 |

| 6.3 | Amplitude adjustment range              | 12 |

| 6.4 | Vertical DC reference                   | 12 |

| 6.5 | Linearity correction                    | 12 |

| 7.  | LAY-OUT HINTS.                          | 12 |

| 8.  | ADJUSTING PROCEDURE                     | 12 |

| 8.1 | Horizontal frequency                    | 13 |

| 8.2 | Vertical frequency                      | 13 |

| 8.3 | Vertical amplitude and horizontal phase | 13 |

| 8.4 | Vertical linearity.                     | 13 |

| 9.  | COMPONENT LIST                          | 15 |

#### Page

Page

# **TECHNICAL INFORMATION**

### 1. ABSTRACT

The system evolution in the monitor field leads to develop suitable I.C.'s whose performances and characteristics are mainly monitors oriented rather than TV oriented. The automatic frequencies raster preset of the monitor by computer and optical equipments leads to the adoption of Digital to Analog converters in order to set the different parameters, and consequently all regulation must be DC compatible.

High scanning frequency and low jitter are additional factors that characterize the quality and the resolution of the monitor. In this note new circuit solutions on silicon, concerning the monitor field, are described. In a single I.C., making use of TTL compatible synchro pulses, horizontal and vertical processing functions and vertical ramp generation are implemented.

### 2. INTRODUCTION

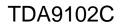

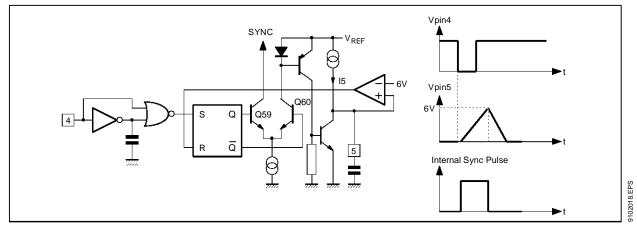

In Figure 1 is shown the block diagram of TDA9102C.

Horizontal frequency and phase as well as vertical frequency, amplitude and linearity are all DC adjustable on different terminals. The horizontal phase adjustment within  $\pm$  45° is implemented on first PLL (sync-oscillator) rather than on the second PLL (flyback-oscillator) allowing the raster to be centered in case of no standard phase sync position.

An additional feature makes the raster phase independent by the duty-cycle of the input synchronizing pulse thanks to an internal shaper circuit generating a standard sync pulse starting from the leading edge of input signal.

The vertical amplitude changes depending on a voltage amplifier whose gain is set on Pin 16; the peak to peak voltage of the sawtooth does not influence its average value which is maintained constant.

The current capability of the horizontal output stage (Pin 7) is such to directly drive an external darlington used as line power switch.

Since part of the jitter effect is due to the internal voltage reference circuits, an external pin connected to the  $V_{CO}$  supply voltage is got available for noise filtering (Pin 19).

#### **3. FUNCTIONAL DESCRIPTION**

Here following are briefly described all the functional blocks of TDA9102C.

#### 3.1 Horizontal oscillator

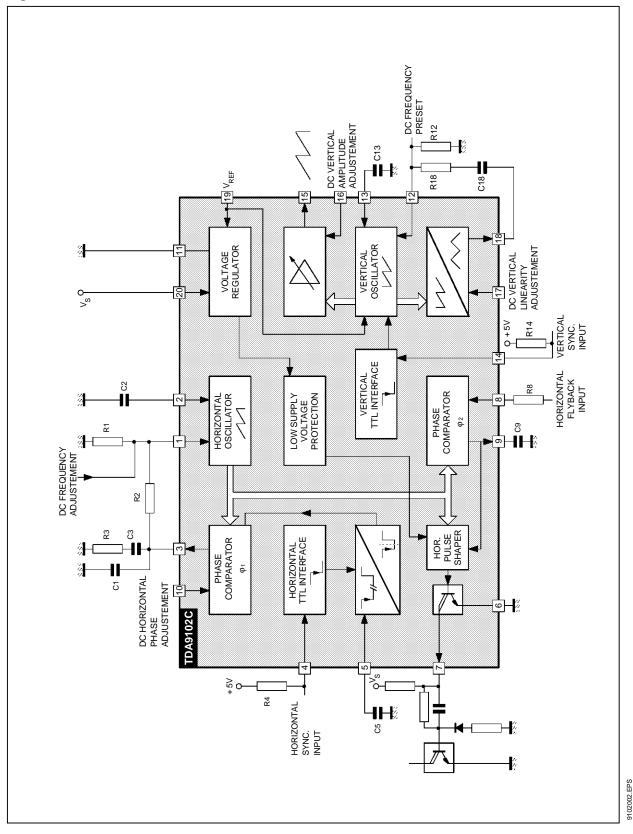

The circuit in Figure 2 is a Current Controlled

Oscillator, it works charging and discharging the capacitor at pin 2 between two thresholds  $V_{S1} = 2.5V$  and  $V_{S2} = 6.5V$  coming from an internal resistor divider. This one is also used to provide a voltage reference at pin 1 ( $V_1 = 3.5V$ ) by means of a unity gain amplifier.

An external resistor connected between Pin 1 and ground sets the current reference.

This current is mirrored with 0.5 : 1 ratio to charge the capacitor  $C_0$  at Pin 2, and with 2 : 1 ratio to discharge  $C_0$ .

The charging and discharging time ratio will result in 3 : 1.

The differential switch  $Q_{22}$ - $Q_{23}$  is driven by a S-R flip-flop, which changes its state every time that the peak of the triangular waveform reaches one of the two thresholds  $V_{S1}$  or  $V_{S2}$ .

#### 3.2 Horizontal synchronism shaper circuit

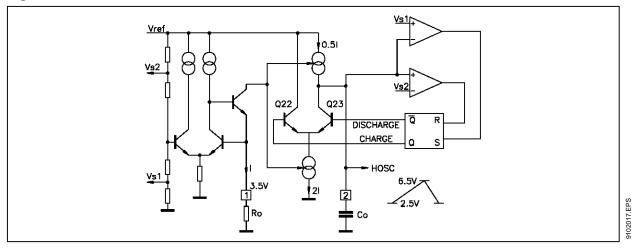

The electric diagram shown in Figure 3 can be divided in three stages. The first of which is a negative edge detector able to set the S-R flip-flop each time that a negative edge of the sync pulse is applied to the input (Pin 4).

The second one is a differential stage that feeds the first phase comparator ( $\phi$  1).

The third stage uses an external capacitor to produce a ramp on the Pin 5. As soon as the peak of the ramp reaches the internal threshold (6V) the external capacitor is suddenly discharged and the flip-flop is reset.

The horizonal sync pulse width on the collector of  $Q_{59}$  will depend on the value of the capacitor at Pin 5.

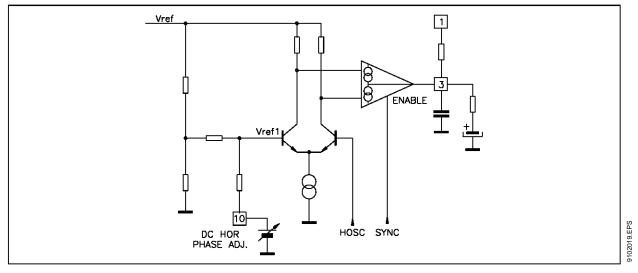

# 3.3 First phase comparator ( $\phi$ 1) and phase adjustment interface circuit

In the circuit of Figure 4, a comparator squares the horizontal waveform using as voltage reference Vref1 which represents the output of the phase adjustment interface circuit.

If the voltage at Pin 10 changes in the range from 0.5V to 4.5V, the phase will shift of  $\pm$  45° between the sync and the middle of H-sawtooth (consequently middle of H-flyback).

The rectangular waveforms that are the outputs of first differential amplifier are applied to another differential stage which is activated only during the internal horizontal sync pulse coming from the horizontal sync shaper circuit (see Figure 3).

The product in terms of current of the sync signal and the oscillator signal is available at Pin 3.

Two clamps limit the maximum voltage range of Pin 3 (from 1V to 6V) and consequently the hold in range of the CCO.

SGS-THOMSON MIGROELECTRONIGS

# Figure 2

# Figure 3

# Figure 4

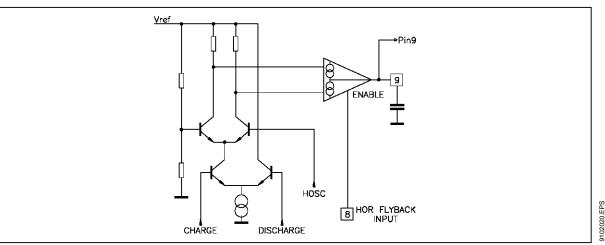

# 3.4 Second phase comparator ( $\phi$ 2) between flyback and oscillator

This circuit recovers dynamically the deflection delay of line output transistor.

The flyback pulse applied to Pin 8 (see Figure 5) is detected and clamped at a voltage level of 0.7V.

This circuit is similar to  $\varphi$  1, the substantial differences are two, the input pulse is the flyback pulse instead of sync pulse and the first differential stage is activated by S-R flip-flop of horizontal oscillator.

The  $\varphi$  2 output acts on the horizontal output stage in order to shift the output pulse to recover the deflection delay.

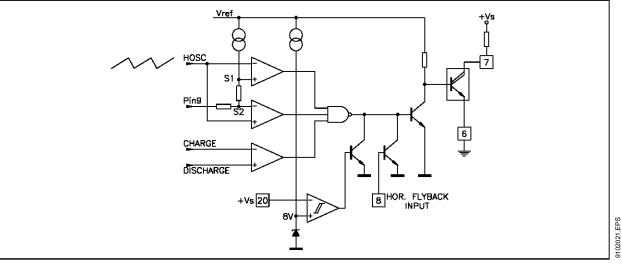

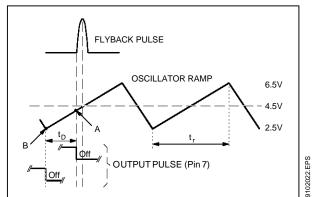

# 3.5 Phase shifter, output stage and start up circuit

The storage time  $t_S$  of the line output transistor is recovered by advancing the leading edge of the output pulse of ts with respect to the phase of the sync reference.

The triangular oscillator waveform (Figure 6a) is compared with internal threshold  $S_1$  and  $S_2$  whose voltages depend upon the voltage level present at the output of phase comparator  $\varphi$  2 (Pin 9).

The voltage difference  $S_1$ - $S_2$  is constant and this value fixes the duty-cycle of the horizontal output pulse present at Pin 7.

During the positive slope of the oscillator the output pulse (Pin 7) is low when the triangular waveform voltage is in the voltage range established by  $S_1$  and  $S_2$ ; whereas during the negative slope of the

#### Figure 5

oscillator the output pulse is always at high level thanks to a comparator driven by S-R flip-flop of horizontal oscillator.

As shown in Figure 6a, a transistor insures that the output pulse is low when the flyback pulse is present (this feature can be used to simplify X-ray protection).

At the switch on, the horizontal output stage (Pin 7) is inhibited until the power supply does not overcome 8 V.

About the maximun allowable delay, it depends on the flyback time and the working frequency (see Figure 6b).

The PLL2 works in such a way as to maintain the middle of the flyback exactly in correspondence with the crossing between of the  $V_{REF} = 4.5V$  and the oscillator ramp.

Then if you suppose to have zero delay time, the switch-off edge of the output pulse will rise at point "A" now if the delay time increases the switch-off edge will move to point "B" to recover the delay.

The equation to calculate the  $t_D$  with a good approximation is the following :

Maximum Allowable Delay :

$$t_D = \frac{t_r}{2} - \frac{t_{FLY}}{2}$$

where  $t_R$  is the rise time of the horizontal ramp = 3/4 T and  $t_{FLY}$  is the flyback time.

The typical value of the horizontal duty cycle of the TDA9102C is 41%.

#### Figure 6a

#### Figure 6b

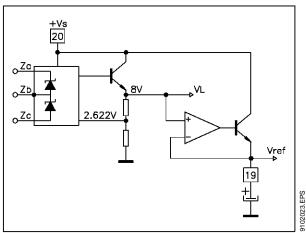

#### 3.6 Voltage regulator 8 V

The voltage reference, Figure 7, is a band-gap circuit that allows on the output a voltage reference equal to 2.622V that means a voltage  $V_L = 8V$ .

#### Figure 7

By means of zener zap is possible to adjust, during the testing, the voltage reference from  $\pm$  6% into a ± 2% range.

$V_{I}$  feeds all the circuits of the vertical side and, by means of a unity gain amplifier, provides a voltage reference (VREF) at Pin 19 to supply all the circuits of the horizontal side.

The unity gain amplifier is necessary to avoid all the possible interactions between the horizontal and vertical sections.

Moreover, to minimize jitter on the horizontal oscillator, is possible to connect an external capacitor between Pin 19 and ground.

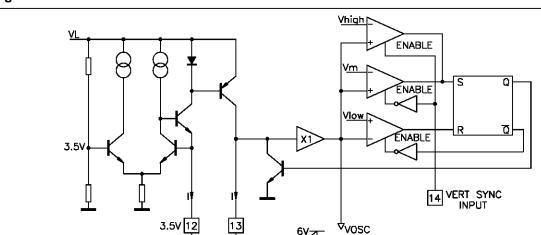

#### 3.7 Vertical oscillator

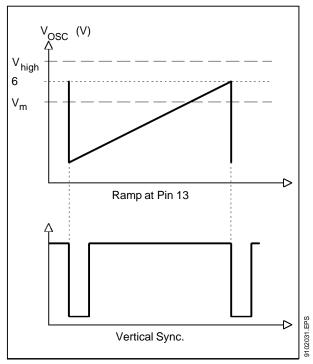

A new concept of vertical oscillator is implemented in this I.C. whose resistor divider, used to set the lower and higher thresholds ( $V_{low} = 2V$ ;  $V_{high} = 6.8V$ ), is not commutated.

The circuit shown in Figure 8 works charging an external capacitor connected at Pin 13 with a current set at Pin 12 and reflectd to Pin 13 through a current mirror.

As soon as the ramp gets V<sub>m</sub> or V<sub>high</sub> the capacitor is quickly discharged by a darlington, the voltage on the capacitor will fall down till to get the lower threshold; at this point the darlington will be driven off and the current will charge again the capacitor.

A buffer is used to decouple the ramp generator from other circuits (like linearity correction and amplitude regulation circuits).

The lower threshold is detected by a differential stage whose current generator is only activated during the discharge phase.

#### Figure 8

A comparator detects the higher threshold corresponding to the free running frequency; if no sync pulse (negative edge) is applied on Pin 14, this stage is continually fed and the capacitor at Pin 13 is discharged when the vertical ramp reaches V<sub>high</sub>.

If the sync pulse is present the previous comparator will be inhibited and another comparator, which has the threshold at 5.2V (V<sub>m</sub>), will be activated.

This last comparator, when it is set going, is able to cause the discharge of the capacitor at Pin 13 if the vertical ramp is between the thresholds Vm and  $V_{high}$ .

In this way the vertical synchronization is established.

To guarantee that the vertical oscillator is locked in the middle of the pull-in range is necessary to adjust the current at Pin 12 until the peak of the vertical sawtooth, in locking condition, reaches the voltage equal to:

$$V_{P} = \frac{V_{m} + V_{high}}{2} = 6 V$$

that means  $V_{pp} = 4V$ .

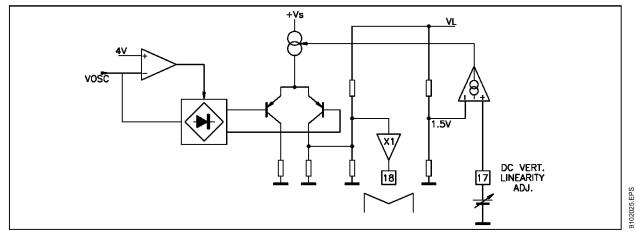

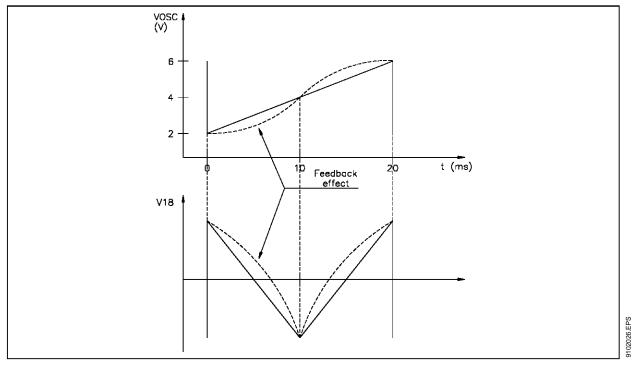

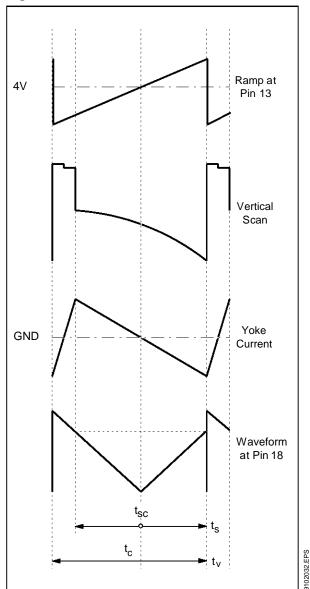

#### 3.8 S Correction circuit and DC linearity adjustment

The circuit which is used to realize a new concept of vertical linearity regulation is shown in Figure 9. A comparator rectifies the vertical sawtooth using as voltage reference a fixed value (4V) that is the average value of sawtooth.

This squared signal is used to drive a particular configuration of differential stage in order to obtain, in terms of current, a triangular waveform which inverts its slope just when the original sawtooth crosses the voltage reference.

91 02024.EPS

This current signal is converted in voltage by a resistor divider and transferred on Pin 18 through a buffer.

The peak to peak voltage on this pin depends on the maximum current that the output differential stage is able to handle, the value of this current can be externally regulated by means of Pin 17 through a transconductance amplifier.

An external feedback resistor in series to a capacitor (to avoid any DC offset) must be connected between Pins 18 and 12 in order to obtain the proper S correction as shown in Figure 10.

#### 3.9 Vertical amplitude regulation circuit

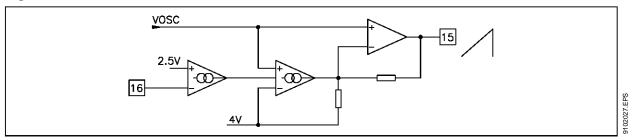

This function has been implemented using the circuit configuration that can be seen in Figure 11. It consists of an Op-Amp in non inverting input configuration and of a variable gain OTA whose gain can be set by means of the Pin 16 through a transconductance amplifier.

#### Figure 10

Both the inputs of the two circuit handle the vertical ramp and the output of the multiplier is fed back to the inverting input.

The control circuit is a transconductance amplifier that modulates the current of the variable gain OTA depending on the DC voltage applied on Pin 16.

This circuit guarantees a gain adjustment of  $\pm\,20\%$  around the nominal value.

#### 4. CONCLUSION

This new I.C. can be considered as a first step towards a new generation of serial bus compatible LSI circuits in which additional logic function can be implemented and all the D/A converters can be included.

It is assembled in 20 pins DIL plastic package able to dissipate the 0.7W required by a typical application.

#### Figure 11

#### **APPLICATION INFORMATION**

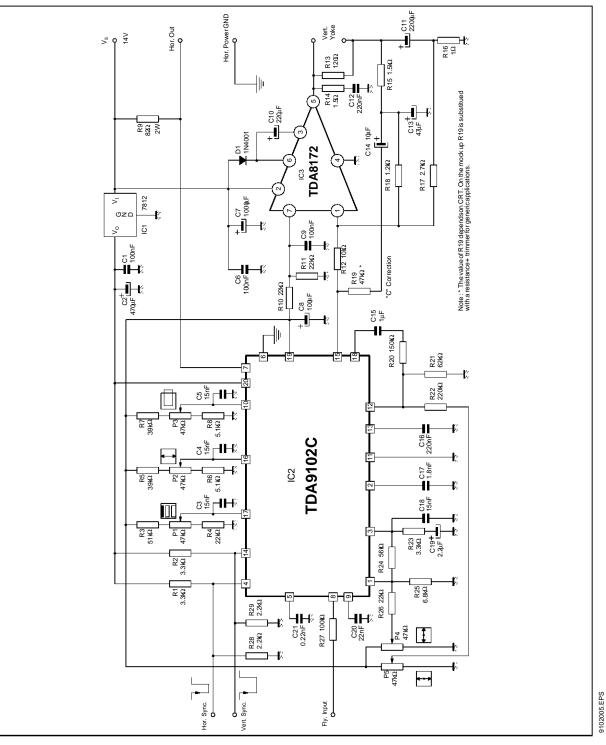

In Figure12 is shown a typical application of the TDA9102C with the TDA8172, which is a vertical booster; for further information regarding TDA8172 consult the note :

#### Figure 12

SGS-THOMSON "Vertical Deflection Stages for TV and Monitor" by A. MESSI

All the information is referred to the above mentioned figure.

SGS-THOMSON MICROELECTRONICS

## 5. HORIZONTAL SECTION

#### 5.1 Frequency

The device is able to work from 15kHz to 100kHz. The free running frequency is fixed by the resistor at Pin 1 (R<sub>25</sub>) and by the capacitor at Pin 2 (C<sub>17</sub>) with the following formula:

$$f_{\rm O} = \frac{1}{K_{\rm O} \ x \ R_{25} \ x \ C_{17}}$$

where K<sub>O</sub> is typically  $3.0476 \pm 5\%$  (see data-sheet). In the aplication of Figure 12, using  $R_{25} = 6.8k\Omega$  and  $C_{17} = 1.8nF$ , we obtain:

$$f_{\rm O} = \frac{10^6}{3.0476 \, \text{x} \, 6.8 \, \text{x} \, 1.8} = 26.808 \, \text{kHz}$$

The maximum available current at Pin 1 is 1mA, so it must be  $\frac{V_1}{R_{25}} \le 1$ mA.

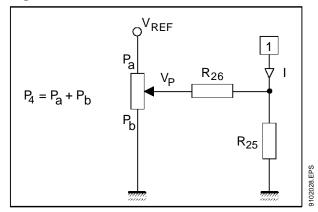

By means of trimmer P<sub>4</sub>, it is possible to adjust the horizontal free running frequency, that changes accordingly with the following formula:

$$f_{H} = f_{O} \ (1 - \frac{(V_{p} - V_{1}) \ / \ R_{26}}{V_{1} \ / \ R_{25}})$$

where  $0 \le V_p \le 8V$  is the voltage at the central point of the trimmer (see Figure 13).

Figure 13

# 5.2 Pull-in range

This range is determined by the ability of the first comparator ( $\phi$  1) to correct the difference between the sync frequency and the free running frequency and it is set by R<sub>24</sub> and R<sub>25</sub>.

$$f_{pull-in} = f_O \; \frac{\mid V_3 - V_1 \mid / \; R_{24}}{V_1 \; / \; R_{25}}$$

$|V_3 - V_1|$  is typically 2.5V, while  $V_1 = 3.5V$ .

This is the theoretical value calculated if the frequency adjustment is disconnected.

In the application inf Figure 12 we have:

$$f_{\text{pull-in}} = 26808 \, \frac{2.5}{3.5} \cdot \frac{6800}{56000} = \pm \, 2.3 \text{kHz}$$

When the frequency adjustment is connected the pull-in range changes due to the fact that in parallel with  $R_{25}$  are connected  $R_{26} + P_b$  (see Figure 13).

When the device is synchronized and perfectly tuned,  $V_3 = V_1$  and the  $\varphi$  1 will work in the best way.

$C_{17}$ , on the contrary of  $R_{25}$ , is influential only for the free running frequency of the horizontal oscillator; it has no effect on the pull-in range, which doesn't change in percentage with respect to the free running frequency.

If you change the horizontal frequency changing  $R_{25}$  the pull-in range changes accordingly with the previous formula.

# 5.3 Internal sync. width

The internal sync. pulse is made by current generator ( $I_5$ ) that charges an external capacitor at Pin 5 ( $C_{21}$ ) up to the trigger threshold  $V_5 = 6V$ .

$$t_5 = \frac{C_{21} \times V_5}{I_5}$$

$t_5 = 1 / (12 \times f_0)$  is recommended.

# 5.4 Phase adjustment range

The voltage range accepted at Pin 10 is from 0.5V to 4.5V, so the resistor divider must be dimensioned to supply these values.

In our application we have :

$$V_{10 \text{ min}} \begin{vmatrix} = \frac{V_{19}}{R_7 + P_3 + R_8} & R_8 \\ = \frac{8}{39 + 47 + 5.1} & 5.1 \\ = 0.447 V \end{vmatrix}$$

$$V_{10 \text{ max}} \begin{vmatrix} = \frac{V_{19}}{R_7 + P_3 + R_8} (P_3 + R_8) \\ = \frac{8}{39 + 47 + 5.1} 52.1 \\ = 4.575 V \end{vmatrix}$$

#### 5.5 Flyback input

The resistor in series at Pin 8 ( $R_{27}$ ) must be dimensioned in order to have an input current included between 0.7mA and 2mA (typ 1mA), according with the following formula:

$$R_{27} = \frac{V_{fly} - 0.6V}{1mA}$$

#### 6. VERTICAL SECTION

#### 6.1 Frequency

The device is able to work form 30Hz to 120Hz.

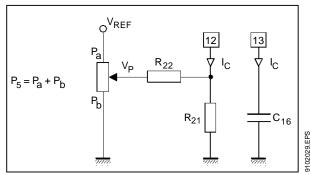

The free running frequency is fixed by  $R_{21}$  and  $C_{16}$ . The formula to calculate the free running frequency is the following:

$$f_v = \frac{I_C}{(V_{high} - V_{low}) \times C_{16}}$$

but

$$I_{C} = I = \frac{V_{12}}{R_{21}} \le 0.5 \text{mA}$$

then

$$f_v = \frac{V_{12}}{(V_{high} - V_{low}) \ x \ C_{16} \ x \ R_{21}}$$

where  $V_{12} = 3.5V$ ,  $V_{high} = 6.8V$  and  $V_{low} = 2V$ . In the application proposed the free running frequency is:

$$f_v = \frac{3.5 \times 10^6}{(6.8 - 2) \times 220 \times 62} = 53.4 \text{Hz}$$

With the trimmer  $P_5$  is possible to change the current that charges  $C_{16}$  and consequently to change the free running frequency.

The current in  $C_{16}$  due to this correction become:

$$I_C = \frac{V_{12}}{R_{21}} - \frac{V_P - V_{12}}{R_{22}}$$

where  $0 \le V_P \le 8V$  is the voltage at the central point of the trimmer (see Figure 14).

#### Figure 14

It is easy to substitute the new  $I_C$  in the formula in order to obtain the new free running frequency.

# 6.2 Pull-in range

The vertical pull-in range is fixed by internal thresholds.

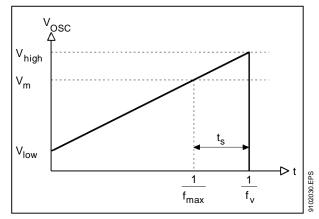

With reference to Figure 15 :

we can write :

$f_{pull}$  - in =  $f_{max}$  -  $f_{v}$

$$f_{max} = \frac{1}{t_v - t_s}$$

$$t_{s} = \frac{(\ V_{high} - V_{m}\ )}{(\ V_{high} - V_{low}\ )} \ x \ t_{v} = K_{14} \ x \ t_{v}$$

the value of K<sub>14</sub> is 0.333 (see data-sheet).

#### Figure 15

#### 6.3 Amplitude adjustment range

The voltage range accepted at pin 16 is from 0.5V to 4.5V.

So the resistor divider must be dimensioned to supply these values.

In our application we have:

$$V_{16min} \begin{vmatrix} = \frac{V_{19}}{R_5 + P_2 + R_6} & R_6 \\ = \frac{8}{39 + 47 + 5.1} & 5.1 \\ = 0.447V \end{vmatrix}$$

$$V_{16max} \begin{vmatrix} = \frac{V_{19}}{R_5 + P_2 + R_6} (P_2 + R_6) \\ = \frac{8}{39 + 47 + 5.1} 52.1 \\ = 4.575 V$$

This system allows a vertical ramp amplitude variation of  $\pm$  20% around the nominal value; the value of amplitude of vertical ramp at Pin 15 can be determined with the following formula:

$$V_{15 \text{ pp}} = [K_{16} (V_{16} - 2.5) + K_{15}] V_{13 \text{pp}}$$

Where  $K_{15}$  is typically 1 and  $K_{16}$  is typically 0.1 (as you can see on the data-sheet).

#### 6.4 Vertical DC reference

The average value of the vertical ramp at Pin 15 is the half of  $V_{19}$ , then with a resistive divider this DC voltage can be used as reference for the vertical booster as shown in Figure 12.

For a best noise immunity we suggest to filter  $V_{19}$  with an electrolytic capacitor.

#### 6.5 Linearity correction

The "S" correction is performed with the new concept described in chapter 3.8.

The adjustment is obtained varying the DC voltage at Pin 17 from 1.5 to 4.5V, then the resistor divider (R3, P1 and R4) must be dimensioned for obtaining this range of values.

In our application we have:

$$V_{17min} \begin{vmatrix} = \frac{V_{19}}{R_3 + P_1 + R_4} \\ = \frac{8}{51 + 47 + 22} \\ = 1.466V \end{vmatrix}$$

$$V_{17max} \begin{vmatrix} = \frac{V_{19}}{R_3 + P_1 + R_4} (P_1 + R_4) \\ = \frac{8}{51 + 47 + 22} 69 \\ = 4.6V \end{vmatrix}$$

The "S" correction is not performed when the voltage at Pin 17 is 1.5V, while it is maximum when the Pin 17 voltage is 4.5V.

You can verify this using the following formula:

$V_{18pp} = K_{18} (V_{17} - 1.5)$

where K<sub>18</sub> is typically 1.

If the CRT requires a higher "S" correction, it is possible to obtain it reducing the value of  $R_{20}$ ; however take care that  $C_{15}$  in series with  $R_{20}$  is a high-pass filter with the purpose to cut only the DC. In our application we have:

.

$$f_{t} = \frac{1}{6.28 \times R_{20} \times C_{15}} = \frac{10^{3}}{6.28 \times 150 \times 1} = 1.06 \text{ Hz}$$

The "C" correction is obtained with a resistor in series to a capacitor connected between Pin 15 and the central point of the vertical DC feedback of vertical booster ( $R_{19}$  and  $C_{14}$ ).

The value of R<sub>19</sub> is strictly dependent on CRT used.

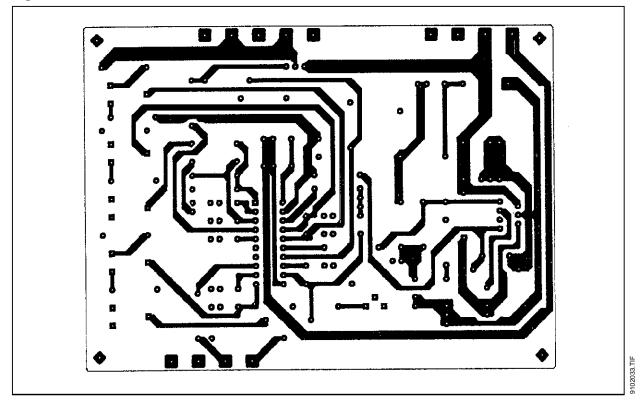

#### 7. LAY-OUT SUGGESTIONS

It is necessary to take care not to connect the horizontal output ground (Pin 6) directly to Pin 11, to avoid horizontal interference on vertical stages.

The 15nF capacitors connected on Pins 10, 16 and 17 have the only aim to filter the DC control voltage against horizontal noise, so they must be connected as close as possible to the above mentioned pins.

# 8. ADJUSTING PROCEDURE

Here following it is shortly described the procedure to adjust horizontal and vertical frequencies, vertical amplitude, linearity and horizontal phase.

Before starting these operations take care that the horizontal and vertical synchronization pulses are properly applied to the device inputs.

#### 8.1 Horizontal frequency

Adjust  $P_4$  in order to obtain  $V_3 = V_1$ ; in this way the horizontal synchronisation is perfect, and the pull-in range is maximum in both directions.

#### 8.2 Vertical frequency

Adjust the vertical ramp amplitude using  $P_5$  in order to have  $4V_{pp}$ ; in this way the vertical frequency value is in the middle of the synchronization range; as shown in Figure 16.

This operation is important because some internal circuits are dimensioned for a  $4_{Vpp}$  ramp.

#### Figure 16

#### 8.3 Vertical amplitude and horizontal phase

Looking at the display correct  $P_2$  for the right vertical amplitude and adjust  $P_3$  in order to have the correct horizontal phase.

#### 8.4 Vertical linearity

If the vertical ramp at Pin 13 is correctly set the central point of the "M" waveform at Pin 18 will be at the center of the scan; in other case, using  $P_5$ , lead the central point of "M" in correspondence of the scan center (see Figure 17).

where :  $t_S = scan time$  $t_V = 1/f_V = vertical period$  $t_{SC} = scan centre$  $t_C = period centre$

In this way the S linearity correction has a uniform behaviour on the top and bottom sides of the CRT.

Now looking at the display, adjust  $P_1$  to obtain a right S correction and select  $R_{19}$  value to optimise the C correction.

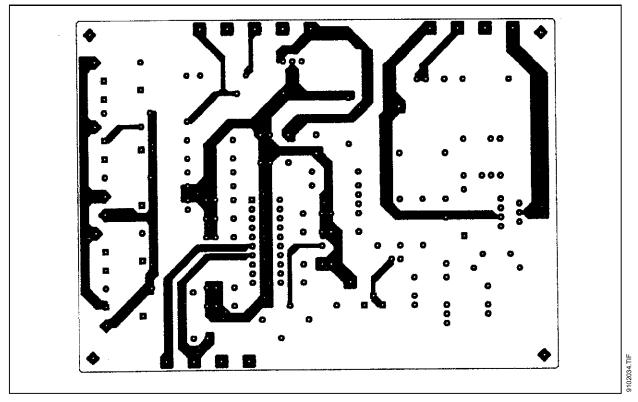

# Figure 18 : Solder Side

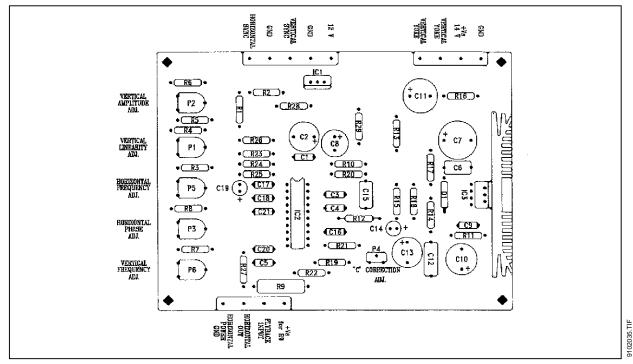

Figure 19 : Component Side

#### Figure 20 : PCB Layout

#### 9. COMPONENT LIST

| Component                                         | Value        | Component                                                                          | Value        | Component                         | Value        |

|---------------------------------------------------|--------------|------------------------------------------------------------------------------------|--------------|-----------------------------------|--------------|

| R <sub>1</sub> , R <sub>2</sub> , R <sub>23</sub> | 3.3kΩ        | R <sub>20</sub>                                                                    | 150kΩ        | C <sub>10</sub>                   | 220µF / 25V  |

| R <sub>3</sub>                                    | 51k $\Omega$ | R <sub>21</sub>                                                                    | 62kΩ         | C <sub>11</sub>                   | 2200µF / 16V |

| R4, R10, R11, R26                                 | 22kΩ         | R <sub>22</sub>                                                                    | 220kΩ        | C <sub>12</sub> , C <sub>16</sub> | 220nF        |

| R <sub>5</sub> , R <sub>7</sub>                   | 39kΩ         | R <sub>24</sub>                                                                    | 56kΩ         | C <sub>14</sub>                   | 10µF / 63V   |

| R <sub>6</sub> , R <sub>8</sub>                   | 5.1kΩ        | R <sub>25</sub>                                                                    | 6.8kΩ        | C <sub>15</sub>                   | 1μF          |

| R <sub>9</sub>                                    | 82Ω / 2W     | R <sub>27</sub>                                                                    | 100kΩ        | C <sub>17</sub>                   | 1.8nF        |

| R <sub>12</sub>                                   | 10kΩ         | R <sub>28</sub> , R <sub>29</sub>                                                  | 2.2kΩ        | C <sub>19</sub>                   | 2.2µF / 63V  |

| R <sub>13</sub>                                   | 120Ω         | P <sub>1</sub> , P <sub>2</sub> , P <sub>3</sub> , P <sub>5</sub> , P <sub>6</sub> | 47kΩ hor.    | C <sub>20</sub>                   | 22nF         |

| R <sub>14</sub>                                   | 1.5Ω         | P4                                                                                 | 47kΩ ver.    | C <sub>21</sub>                   | 220pF        |

| R <sub>15</sub>                                   | 1.5kΩ        | C <sub>1</sub> , C <sub>6</sub> , C <sub>9</sub>                                   | 100nF        | D <sub>1</sub>                    | 1N4001       |

| R <sub>16</sub>                                   | 1Ω           | C <sub>2</sub> , C <sub>13</sub>                                                   | 470µF / 16V  | IC <sub>1</sub>                   | L7812        |

| R <sub>17</sub>                                   | 2.7kΩ        | C <sub>3</sub> , C <sub>4</sub> , C <sub>5</sub> , C <sub>18</sub>                 | 15nF         | IC <sub>2</sub>                   | TDA9102      |

| R <sub>18</sub>                                   | 1.2kΩ        | C <sub>7</sub>                                                                     | 1000μF / 25V | IC <sub>3</sub>                   | TDA8172      |

| R <sub>19</sub>                                   | 33kΩ         | C <sub>8</sub>                                                                     | 100µF / 16V  |                                   |              |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in a I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

#### SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.